1。基質

1。定義と関数

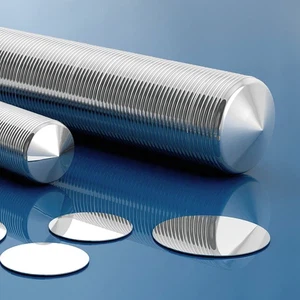

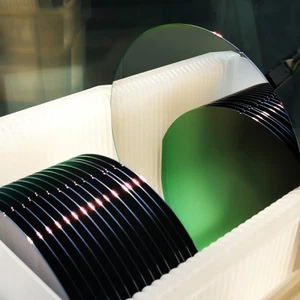

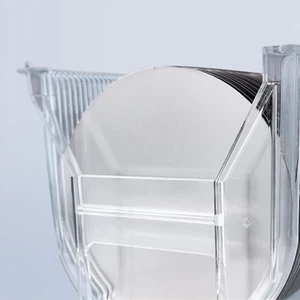

・物理的なサポート:基板は半導体デバイスのキャリアであり、通常は円形または正方形の単結晶ウェーハ(シリコンウェーハなど)です。

・Crystalテンプレート:エピタキシャル層の成長の原子配置のテンプレートを提供して、エピタキシャル層が基質結晶構造(ホモエピタキシャル)または一致(ヘテロエピタキシャル)と一致するようにします。

・電気基盤:基質の一部は、デバイスの伝導(シリコンベースの電力装置など)に直接関与するか、回路を分離するための絶縁体として機能します(サファイア基板など)。

2。主流の基質材料の比較

|

材料 |

特徴 |

典型的なアプリケーション |

|

シリコン(SI) |

低コスト、成熟技術、中程度の熱伝導率 |

統合回路、MOSFET、IGBT |

|

サファイア(al₂o₃) |

断熱、高温抵抗、大きな格子の不一致(GANで最大13%) |

GANベースのLED、RFデバイス |

|

炭化シリコン(原文) |

高い熱伝導率、高い分解面強度、高温抵抗 |

電気自動車電源モジュール、5GベースステーションRFデバイス |

|

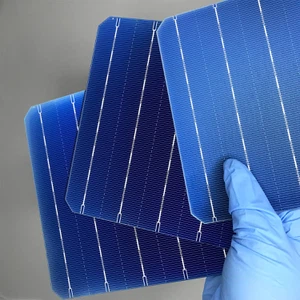

ガリウムアルセニド(GAAS) |

優れた高周波特性、直接バンドギャップ |

RFチップ、レーザーダイオード、太陽電池 |

|

窒化ガリウム(ガン) |

高電子移動度、高電圧抵抗 |

高速充電アダプター、ミリメートルウェーブ通信デバイス |

3。基板選択に関するコア考慮事項

・格子マッチング:エピタキシャル層の欠陥を減らす(例:Gan\/Sapphire Latticeの不一致は13%に達し、バッファ層が必要です)。

・熱膨張係数マッチング:温度変化によって引き起こされる応力亀裂を避けてください。

・コストとプロセスの互換性:たとえば、シリコン基質は成熟したプロセスのために主流を支配します。

2。エピタキシャル層

1。定義と目的

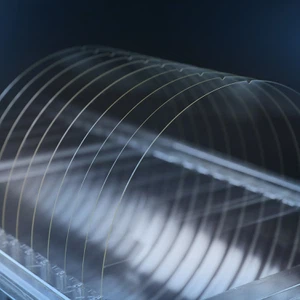

エピタキシャルの成長:原子配置が基質と厳密に整列した化学的または物理的方法による基質表面上の単結晶薄膜の堆積。

コア関数:

- 材料の純度を改善します(基質には不純物が含まれている場合があります)。

- 不均一な構造(GAAS\/algaas Quantum Wellsなど)を構築します。

- 基質の欠陥(SIC基質のマイクロパイプ欠陥など)を分離します。

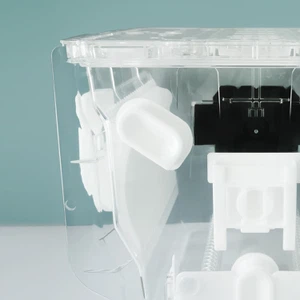

2。エピタキシャル技術の分類

|

テクノロジー |

原理 |

特徴 |

該当する材料 |

|

MOCVD |

金属有機源 +ガス反応(TMGA +nh₃などのGANを生成する) |

化合物半導体、大量生産に適しています |

ガン、ガース、inp |

|

mbe |

超高真空下での分子ビーム層ごとの堆積 |

原子レベルの制御、成長率の低下、高コスト |

超格子、量子ドット |

|

LPCVD |

低圧下でのシリコンソースガス(SIHなど)の熱分解 |

主流のシリコンエピタキシー技術、良好な均一性 |

Si、sige |

|

HVPE |

高温ハリド蒸気相エピタキシー |

厚いフィルム(Gan基板など)に適した高速成長率 |

ガン、Zno |

3.エピタキシャル層設計の重要なパラメーター

- 厚さ:数ナノメートル(量子井戸)から数十ミクロン(電力装置の疫病)まで。

- ドーピング:リン(N型)やホウ素(P型)などの不純物をドーピングすることにより、キャリア濃度を正確に制御します。

- インターフェイス品質:格子の不一致は、バッファー層(GAN\/ALNなど)または緊張した超格子によって緩和する必要があります。

4。ヘテロエピタキシャル成長の課題と解決策

- 格子の不一致:

- 勾配バッファー層:組成を徐々に基質からエピタキシャル層(Algan Gradient層など)に変更します。

- 低温核生成層:低温で薄層を増やしてストレスを軽減します(GANの低温ALN核生成層など)。

- 熱ミスマッチ:同様の熱膨張係数を持つ材料の組み合わせを選択するか、柔軟なインターフェイス設計を使用します。

3.基質とエピタキシーの相乗的適用症例

ケース1:GANベースのLED

基板:サファイア(低コスト、断熱材)。

エピタキシャル構造:

- バッファー層(ALNまたは低温GAN)→格子の不一致の欠陥を減らします。

- n型Gan層→電子を提供します。

- Ingan\/Gan Multi-quantum well→排出層。

- PタイプGAN層→穴を提供します。

結果:欠陥密度は10℃ほど低く、発光効率が大幅に改善されます。

ケース2:SIC Power Mosfet

基質:4H-SIC単結晶(10 kVまでの電圧に耐える)。

エピタキシャル層:

- n型SICドリフト層(厚さ10-100μm)→高電圧に耐える。

- PタイプSICベース領域→制御チャネル形成。

利点:シリコンデバイスよりも90%低い抵抗、5倍高速なスイッチング速度。

ケース3:シリコンベースのGan RFデバイス

基板:高耐性シリコン(低コスト、統合が簡単)。

エピタキシャル層:

- ALN核形成層→SIとGANの間の格子の不一致を緩和します(16%)。

- GANバッファーレイヤー→欠陥をキャプチャし、アクティブ層まで伸びることを防ぎます。

- Algan\/Gan Heterojunction→High電子移動チャネル(HEMT)を形成します。

アプリケーション:28 GHzを超える周波数の5Gベースステーションパワーアンプ。