チップ製造は、現在世界で最も複雑なプロセスです。これは、多くのトップ企業によって実行される複雑なプロセスです。この記事では、このプロセスを要約し、この複雑なプロセスについて包括的かつ一般的な説明をします。

半導体の製造工程は数多くあり、数百、数千のステップがあると言われています。これは誇張ではありません。10億ドルを投資した工場でも、工程のごく一部しか行っていない可能性があります。このような複雑な工程について、この記事では、ウェーハ製造、フォトリソグラフィーとエッチング、イオン注入、薄膜堆積、パッケージングとテストの5つの主要なカテゴリに分けて説明します。

1. 半導体製造プロセス - ウェハ製造

ウェーハ製造は、主に次の 5 つのプロセスに分けられます。

(1)水晶の引き抜き

◈ ドープポリシリコンは1400度で溶解する

◈ 高純度アルゴン不活性ガスを注入

◈ 単結晶シリコンの「種」を溶融物の中に置き、「引き抜く」ときにゆっくりと回転させます。

◈ 単結晶インゴットの直径は温度と抽出速度によって決まります

(2)ウェーハスライスでは、精密な「のこぎり」を使用してシリコンインゴットを個々のウェーハに切断します。

(3)ウェーハ研磨、エッチング

◈ スライスされたウェーハは、回転式グラインダーとアルミナスラリーを使用して機械的に研磨され、ウェーハ表面が平坦かつ平行になり、機械的欠陥が減少します。

◈ 次に、ウェーハを窒化酸/酢酸溶液でエッチングして微細な亀裂や表面の損傷を除去し、その後、一連の高純度 RO/DI 水浴で処理します。

(4)ウェーハ研磨・洗浄

◈ 次に、CMP(化学機械研磨)と呼ばれる一連の化学機械研磨プロセスでウェーハを研磨します。 ◈ 研磨プロセスには通常、次第に細かくなるスラリーを使用した2~3回の研磨ステップと、RO/DI水を使用した中間洗浄が含まれます。 ◈ 最終洗浄は、SC1溶液(アンモニア、過酸化水素、RO/DI水)を使用して実行され、有機不純物と粒子が除去されます。次に、HFを使用して自然酸化物と金属不純物が除去され、最後にSC2溶液によって超清浄な新しい自然酸化物が表面に成長します。(5)ウェーハエピタキシャル処理

◈ エピタキシャル成長 (EPI) は、高温で単結晶シリコン基板上に気相から単結晶シリコンの層を成長させるために使用されます。

◈ 気相から単結晶シリコン層を成長させるプロセスは、気相エピタキシー (VPE) と呼ばれます。

SiCl4 + 2H2 ↔ Si + 4HCl

SiCl4(四塩化ケイ素)

反応は可逆的であり、つまり HCl を加えると、シリコンはウェーハの表面からエッチングされます。

Siを生成するもう一つの反応は不可逆的である:SiH4 → Si + 2H2 (シラン)

◈ EPI 成長の目的は、基板上に電気的に活性なドーパントの濃度が異なる(通常は低い)層を形成することです。たとえば、P 型ウェーハ上の N 型層などです。

◈ ウェーハ厚さの約3%。

◈ 後続のトランジスタ構造への汚染はありません。

2. 半導体製造プロセス - フォトリソグラフィー 近年よく話題になるフォトリソグラフィー装置は、数あるプロセス装置のうちの 1 つにすぎません。フォトリソグラフィーにも、多くのプロセス ステップと装置があります。

(1)フォトレジストコーティング

フォトレジストは感光性材料です。少量のフォトレジスト液をウェーハに加えます。ウェーハを1000〜5000 RPMの速度で回転させ、フォトレジストを2〜200umの厚さの均一なコーティングに広げます。フォトレジストには、ネガとポジの2種類があります。ポジティブ:光にさらされると複雑な分子構造が壊れ、溶解しやすくなります。ネガティブ:露出により分子構造がより複雑になり、溶解しにくくなります。各フォトリソグラフィーステップに含まれる手順は次のとおりです。◈ ウェーハを洗浄する◈ バリア層SiO2、Si3N4、金属を堆積する◈ フォトレジストを塗布する◈ ソフトベーク◈ マスクを位置合わせする◈ グラフィック露光◈ 現像◈ ベーク◈ エッチング◈ フォトレジストを除去する (2) パターンの準備 パターンの準備 IC設計者は、CADソフトウェアを使用して各層のパターンを設計します。 次に、レーザー パターン ジェネレーターまたは電子ビームを使用して、パターンが光学的に透明な石英基板 (テンプレート) に転写されます。

(3)パターン転写(露光)ここでは、フォトリソグラフィー装置を使用して、テンプレートからチップ層にパターンを投影してコピーします。

(4)現像とベーキング ◈ 露光後、ウェハーは酸またはアルカリ溶液で現像され、フォトレジストの露光された部分が除去されます。 ◈ 露光されたフォトレジストが除去されると、ウェハーは低温で「ベーキング」され、残りのフォトレジストが硬化されます。

3. 半導体製造プロセス - エッチングとイオン注入 (1) ウェットエッチングとドライエッチング ◈ 化学エッチングは、大型ウェットプラットフォームで行われます。 ◈ さまざまな種類の酸、塩基、苛性溶液を使用して、さまざまな材料の選択された領域を除去します。 ◈ BOE(緩衝酸化物エッチング剤)は、フッ化アンモニウムで緩衝されたフッ化水素酸から作られ、下にあるシリコンまたはポリシリコン層をエッチングせずに二酸化ケイ素を除去するために使用されます。 ◈ リン酸は、シリコン窒化物層のエッチングに使用されます。 ◈ 硝酸は、金属のエッチングに使用されます。 ◈ フォトレジストは、硫酸で除去されます。 ◈ ドライエッチングの場合、ウェーハはエッチングチャンバーに配置され、プラズマによってエッチングされます。 ◈ 作業員の安全が主な懸念事項です。 ◈ 多くの工場では、エッチングプロセスを実行するために自動化された装置を使用しています。 (2) レジスト剥離

その後、フォトレジストはウェハーから完全に剥がされ、ウェハー上に酸化物パターンが残ります。

(3)イオン注入

◈ イオン注入により、ウェーハ上の既存の層内の特定の領域の電気特性が変化します。

◈ イオン注入装置は、高電流加速管とステアリングおよびフォーカス磁石を使用して、特定のドーパントのイオンをウェーハ表面に照射します。

◈ ドーピング化学物質が表面に堆積し、表面に拡散する間、酸化物はバリアとして機能します。

◈ シリコン表面はアニール処理のために 900 度に加熱され、注入されたドーパントイオンがシリコンウェーハ内にさらに拡散します。

4. 半導体製造プロセス - 薄膜堆積

薄膜形成には多くの方法と内容があり、以下で一つずつ説明する。(1)シリコン酸化物

シリコンが酸素中に存在すると、SiO2は熱的に成長します。酸素は酸素または水蒸気から来ます。周囲温度は900〜1200度である必要があります。発生する化学反応は

Si + O2 → SiO2

Si +2H2O ->SiO2 + 2H2

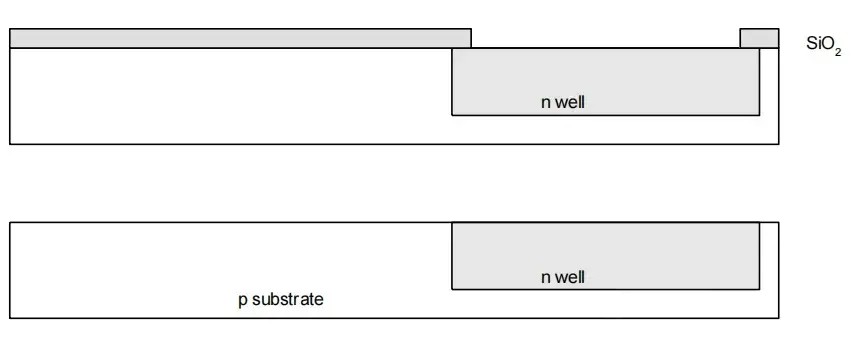

選択酸化後のシリコンウェーハの表面を下図に示します。

酸素と水は両方とも既存の SiO2 を拡散し、Si と結合して追加の SiO2 を形成します。水 (蒸気) は酸素よりも拡散しやすいため、蒸気ははるかに速く成長します。

酸化物は、トランジスタ ゲートを形成するための絶縁層およびパッシベーション層を提供するために使用されます。乾燥酸素は、ゲートと薄い酸化物層を形成するために使用されます。蒸気は、厚い酸化物層を形成するために使用されます。絶縁酸化物層は通常 1500nm 程度で、ゲート層は通常 200nm から 500nm の間です。

(2)化学蒸着

化学蒸着法(CVD)は、気体化合物の熱分解や反応によって基板の表面に薄膜を形成します。

CVD反応器には3つの基本的なタイプがあります: ◈ 大気化学気相成長法

◈ 低圧CVD(LPCVD)

◈ プラズマCVD(PECVD)

低圧CVDプロセスの概略図を以下に示します。

CVDの主な反応プロセスは以下のとおりです。

i). Polysilicon PolysiliconSiH4 ->Si + 2h2 (600度)

堆積速度 100 - 200 nm /分

リン(ホスフィン)、ホウ素(ジボラン)、またはヒ素ガスを追加できます。ポリシリコンは、堆積後に拡散ガスでドーピングすることもできます。

ii). 二酸化ケイ素

SiH4 + O2→SiO2 + 2h2 (300 - 500度)

SiO2 は絶縁体またはパッシベーション層として使用されます。より良い電子フロー性能を得るために、通常はリンが追加されます。

iii). 窒化ケイ素

3SiH4 + 4NH3 ->Si3N4 + 12H2

(シラン) (アンモニア) (窒化物)

(3)スパッタリング

ターゲットにAr+などの高エネルギーイオンを照射すると、ターゲット内の原子が移動して基板に輸送されます。

アルミニウムやチタンなどの金属をターゲットとして使用することができる。(4)蒸発

Al または Au (金) を蒸発点まで加熱すると、蒸気が凝縮してウェハーの表面を覆う薄い膜が形成されます。

次の例では、フォトリソグラフィ、エッチングからイオン堆積まで、シリコン ウェハー上の回路が段階的にどのように形成されるかを詳しく説明します。

5. 半導体製造プロセス - パッケージングテスト(後処理)

(1)ウェハテスト最終的な回路準備が完了した後、ウェハ上のテストデバイスを自動プローブテスト方式でテストし、不良品を除去します。

(2)ウェーハダイシングプローブテスト後、ウェーハを個々のチップに切断する。

(3)配線とパッケージング◈個々のチップはリードフレームに接続され、アルミニウムまたは金のリードは熱圧縮または超音波溶接によって接続されます。◈デバイスをセラミックまたはプラスチックパッケージに密封することでパッケージングが完了します。◈ほとんどのチップは、下流のユーザーに送られる前に最終的な機能テストを受ける必要があります。